| 98システム解析スレッド2024年6月 まりも 2024年6月1日(土) 0:28 |

5月は一貫してCyrix486,ハイレゾ関連の話で続きましたが、今月はmate-R? 5月は一貫してCyrix486,ハイレゾ関連の話で続きましたが、今月はmate-R?

ということで先月のウォッチスレッドより−

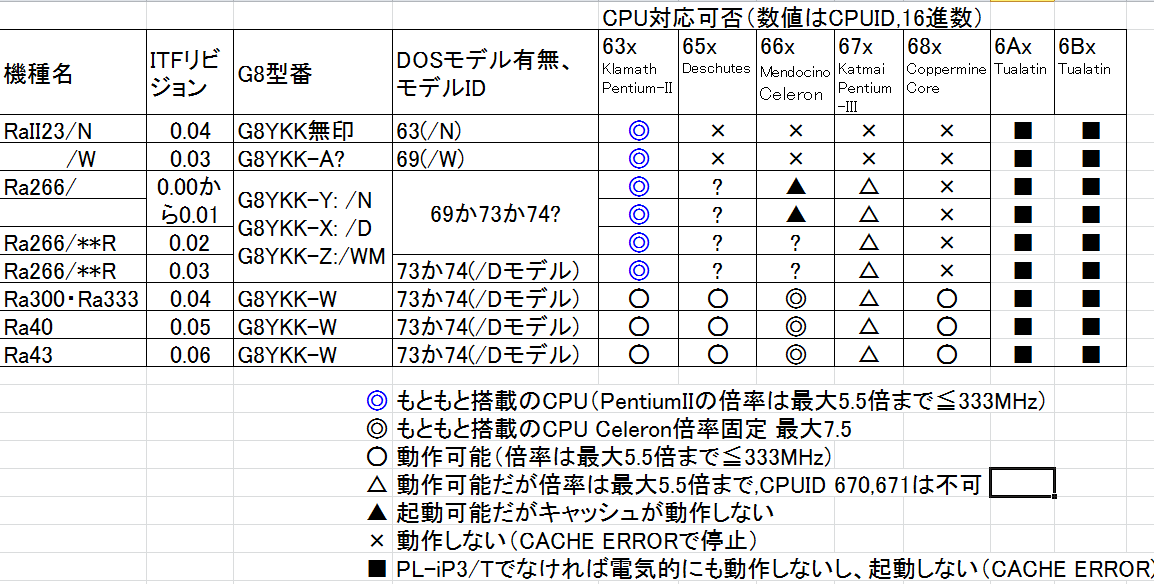

>Katmaiの5.5倍までしか選択肢が無いのはRa266の前期・中期ITFだったような気がしますが

互換性の権化ミイソですのでRa300以降もこれがきちんと残っています。5.5倍以下の加藤舞と全倍率のCopperまいんを載せることができます。

>河童下駄の画像

とりあえずここにチマチマとアップロードして行こうかと思います。まずはRLを押し入れにしまい込んでから、Ra266らしきモノと300を出してくるとします。

>KatmaiはもともとSlot1版しか出ていない

うむむそれはそうでした。S370とSLOT1はcoppermineのほうになります。

|

| 溝1CPU KAZZEZ 2024年6月1日(土) 19:56 |

> Ra300以降もこれがきちんと残っています

Deschutes(SL2S7)のPenIIが366MHz(5.5倍)までで動くのは私もRa40で確認しています。ただRa300以降(Ra266末期も?)ではFSBをチェックするようになったので、下駄でFSB(BSEL?)を騙すことができない溝1版しか存在しないKatmai(ES版は除く?)は動かせなくなったという話があったように記憶しています(ので私は手を出していません)。

FSB100MHz版であればマザー上のチップ抵抗の設定を変えれば簡単な改造で溝1河童も動かせるらしいですが、133MHzに設定するパターンは用意されていないので133MHz版を動かす改造は敷居が高いという話もあったと思います。

結局のところ溝1版の河童733が動いた?という話の説明が付きませんが、Katmaiと違って河童は5.5倍以下だと特別扱いなのでしょうかね?

----

ところで前スレの最後のうなるHMAの件ですが、CPUキャッシュが切れると音で分かるのがちょっぴり便利だったりします。

それでDOS付属のRAMDISK.SYSがCPUリセットをしているらしいことに気付きました。RAMドライブにアクセスすると(元286機では)CPUキャッシュが切れてしまいます。これでは使い物になりませんので、RAMドライブはサードパーティ製のドライバか、95/98付属ののRAMDRIVE.SYSを使ったほうがよさげでした。

まあサードパーティのドライバ(MEMORY SERVERとかMELWAREとか)を使うのであれば、仮想EMM内蔵のキャッシュイネーブラを使えば済む話かもしれませんが。

(23:15追記)

リセットでキャッシュ設定が保持されない286機向けのイネーブラ(PK486SとかMELCSET)で試す限り、RA2では同様の現象は起きませんでしたので、RAMDISK.SYSがリセットしながら読み書きするのは元286機だけの仕様のようです(RXではキャッシュが切れます)。

|

| L2キャッシュ判定設定アルゴリズム(Ra300/333) まりも 2024年6月2日(日) 10:35 |

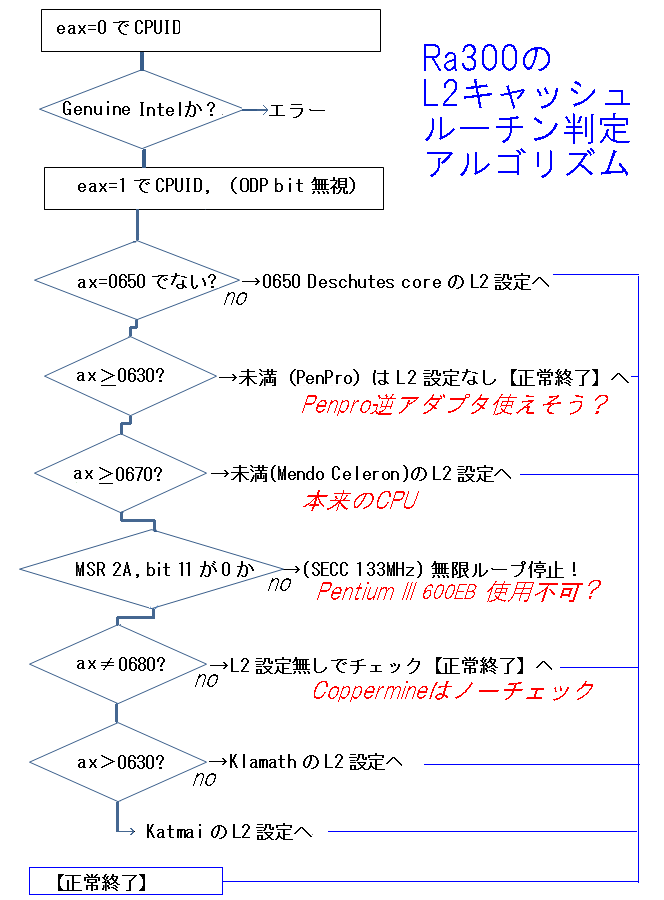

SLOT1のBSEL1の状態をCPU側からMSR 2A で読み出しているんですよね。 SLOT1のBSEL1の状態をCPU側からMSR 2A で読み出しているんですよね。

Ra300の場合、図のようなアルゴリズムでL2キャッシュの判定と設定が行われます。MSR 2A bit11のチェックはよろしくない停止の仕方をします。Socket370のCPUをSLOT-1アダプタで使えば回避できますが。

CPUID=068xのCoppermineはL2設定は完全スルーで必ず成功で終了します。この判定を行う命令が「0680に等しい」というのが曲者です・・・「以上」ではないんです。

そのほかのCPUモデルのL2設定では、何らかの失敗があると黄色CACHE ERRORでL1も切れての起動となりますが、赤色文字でどうにもならなくなるトラップもどっかにあります。KlamathとKatmaiは5.5倍までのチェックが入ります。

Ra40ではこの図とは判定順序がかなり異なっています。Ra43は持っていないのでわかりませんがRa40と同じではないようです。結局機種毎にしらべないといけないのです。しかし処理結果については同じで、さすが互換性の権化ミイソたる所以です。

互換性のせいなのか知りませんが、どえらく汚いアルゴリズムであり、込み入ったプログラムコードでもあります。0630との比較は二度も実行しています。ID値の昇順か降順で素直に切って行けばもっとすっきりできるのに・・・CPUID=06Ax,06BxのTualatinについては、Katimai設定のところに迷い込んで、致命的エラーで放り出されるみたいです。

|

| ソフトから80286機本体に見えないようにする まりも 2024年6月2日(日) 11:55 |

>RAMDISK.SYSがリセットしながら読み書きするのは元286機だけの仕様のよう

ということは、それを判定していそうなところを事前に騙すことで、RAMDISK.SYSが386仕様でリアルモードに戻るようになるのではないでしょうかね。まずシステム共通域0000:0480h、つぎに0000:486でしょうか。

|

| 互換性の所為と云うより かかっくん 2024年6月2日(日) 13:55 |

デモI/O F6hの有無で判定して居たらアクセラにF6hを載せデモしない限り騙せない事に成増

其れがXLやRXどころかEXにもDXにもI/O F6hを積まなかった理由鴨?

で、アクセラにF6hを載せやうにもF2hやF0hとの連携も必要で面倒だから何処も真剣にしなかったのでせう

<del>みいそDOSのRAMDISK.SYSが286でリセットするのわDOSでPMを遣う限り当然の事デスから仕様でせう</del>

アクセラはみいそ的に想定外デスし

一方、窓9xは386+が前提デスからRAMDISK.SYSも386機を前提として居るのでせう

互換性の所為と云うより、再構築を考えず元のコードの空きに増築(パッチ)を繰り返したからの肝?

で、判定が=(Z)で以上(NC)でないのは社内で問題が起こってから再パッチしようと云う考えだったのでせう

アクセラが想定外な以上ユーザサイドで問題が出ても「知った事か」と。

# 以前哀王のMEXのDOS5判定にもあったやうな?>Z判定

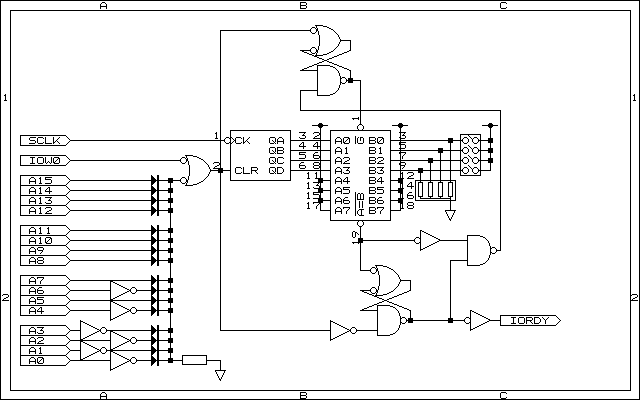

I/O F6hと5Fhの回路デモ検討してみ枡か

286機で5Fhが有る機種は見当が付かないので

|

| システム共通域ではなさそう KAZZEZ 2024年6月2日(日) 14:25 |

> まずシステム共通域0000:0480h、つぎに0000:486

それは考えが及びませんでしたが、やってみたところどっちもだめみたいでしたので、既にご指摘があるように、I/O F6を見ているのかもしれません。

# もともとPK486S.COM(IBM486SLC2用のPK486SQ.COMも同様です)はシステムワークエリアのCPU情報を勝手に書き換えるのは前スレで報告した通りですが、念のためRAMDISK.SYS常駐前にFD-IPLwareでIPLDOS(B)+WAPICO.COMで事前に書き換えてみても同様でした。

> 286でリセットするのわDOSでPMを遣う限り当然

XMSを使うものとしては他にSMARTDRVもありますが、DOS5のSMARTDRV.SYSは組み込んでもキャッシュが切れることは無さそうでした。もっともDOS5の頃のSMARTDRVはバグ持ちでも有名らしいですので、そんなに詳しくは確かめていないのですが。

> Ra300のL2キャッシュルーチン判定アルゴリズム

たしかCovingtonのようにMSRでL2なしを示すビットが立っているとL2設定をスルーしてエラーが出ないという話もあったと思いましたが、この図に載っていないということは、わざわざ分岐先のDeschutes/Mendocino/Klamath/Katmaiそれぞれのルーチンでその部分に関しては同じ処理が行われているということなんでしょうね。

CyrixIII・C3がGenuineIntelチェックさえスルーすれば通るというのも、L2なしビットを立てているからだと思います。Nehemiahなんかは069x(>068x)ですから、普通にL2チェックをすればアウトなはずですよね。

|

| F6hに出力したものをF2hで読んでいるかも まりも 2024年6月2日(日) 15:44 |

|

I/O F6hは、Undoc2 の通りではなく、80386機なのに読み出しではFFhが帰ってきてしまう(読み出せない)機種があります。ミイソ製/ミイソ供給のソフトウェアではF2hの方でA20ラインの再マスクを確認するのではないでしょうかね。80286機に絶対無いF6hのほうを使ってくれていれば、勝手にF6hの回路を作ってしまえばいいのですが、F2hの読み出しでは、騙す回路と元々存在する方とぶつかってしまいそうです。

|

| F2hにも書き込む回路 かかっくん 2024年6月2日(日) 16:55 |

out F6h; in F2hナノは粗間違いナイでせう。386+機は状態が変わり変更後の、(元)286機では変更されず

元の状態の儘返し枡

確かにF6hだけを造った処でF2hにわ反映されませんから却って不整合を産んで仕舞い枡が、斯う成ったら

HOLDサイクルを起こしてF2hにも書き込んで仕舞う回路とか?F2hへの値は任意デスからHOLD(EXHRQ)して

EXHLAが出たらI/O 00F2hとIOWを出してHOLDを止めるとか?

自前でF2hも用意すると指摘通り、のっぺらのやうに打つかって仕舞い枡

# 寧ろA20Mとかをするより回路規模は小さい鴨

但し、逆にA20をマスクする方はド〜してもCPUリセットを伴い枡。此れの回避には付加回路だけでなく基板や

石に手を入れる鹿

ところで、SMARTDRVデスが、XMSを遣いPMを直接遣うのでわナイのでCPUリセットとは直接関係無いデスね

PMを遣うのはXMMデスからXMSを遣いPMを直接遣わないソフトは関係無いと云う事に成増

# 亞、SMARTDRVがXMSを遣うとXMMがPMを遣うのか、とすると(略)

EMBを遣うと必ずCPUリセットするXMZ286やFDXMS286で試してみると?

極論するとEMBとしてPMでわなく他のRAMやストレージを遣うXMMも出来枡。EMSを遣うXMMも有馬す

www.vector.co.jp/soft/dos/hardware/se009690.html

RAMがPMでなければ実装できないのはHMAだけで、EMBは窓やDOSエクステンダで遣うのでない限りPMで

ある必要は無いのデス

|

| I/O 5Fhは単純 かかっくん 2024年6月2日(日) 20:46 |

一方I/O 5Fhの方は単純でI/O 005FhとIOWが有ったらSCLKのnクロック分 一方I/O 5Fhの方は単純でI/O 005FhとIOWが有ったらSCLKのnクロック分

IORDYをLにすれば済み枡。

I/O 5Ehのタイムスタンパの実装は不要(任意)でせう

|

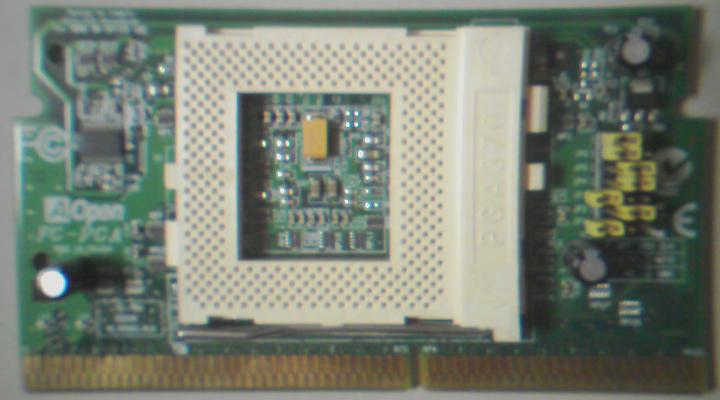

| AOpen FC-PGA KAZZEZ 2024年6月2日(日) 22:14 |

黄色CACHE ERRORを起こす下駄はちょうど5年前に買ったもので、基板上にはAOpenとかFC-PGAとか書いてあるだけです。検索するとここの過去ログ(買ったときの報告)がヒットしたりしますが、どうも「FC-PGA」が型番としか思えません。相変わらず映りが悪いですが写真を載せておきます。

ついでにいくつかの河童(Pen3/Celeron)とMendocinoをRa40で試してみましたが、どれも黄色CACHE ERRORが出る点は同じでした。メモリカウント後かなり間を置いてからエラーが出るので、チェックの終盤でエラーが出ているのかもしれません。

ところで、どるログを検索するとMendocinoでも黄色CACHE ERRORを起こす下駄もあったそうで、やはりキャッシュ有効化で動く点も同じようです。L2チェック時にだけ電気的相性が出るのでしょうか?

ttp://weblabo.griffonworks.net/dorlog/2nddorcom/mmx/352.html

> 80386機なのに読み出しではFFhが帰ってきてしまう

とりあえずRA2/21ではF2/F6ともそうみたいでした。

> XMZ286

DOS付属のRAMDISK.SYSは使えないことになっています。そういえばアイオーのPKXMS.SYSでもRAMDISK.SYSがXMSを見つけられなかったので、HIMEM.SYSでないと動かないというRAMDISK.SYS側の仕様かもしれません。

では、それ以外(SMARTDRVとか)はどうかといえば、どうもXMZ286は元286機であっても実CPUが286でないと動かないようでした。

> no→(SECC 133MHz) 無限ループ停止!

> Pentium III 600E 使用不可?

133MHz版には(更に)Bが付きますので、「13」と「B」は字体が似ていることからこじづけて覚えられるというような話がパソトラにありましたっけ。

> 溝1版の河童733が動いた?という話

自己レスですが、どるこむのログを調べなおしてみたら、ごく初期のCoppermineの中には(CPU側が)FSBチェックに対応していない(MSR 2Aのbit11が立たない)ものが混在しているとのことでした。

ttp://weblabo.griffonworks.net/dorlog/2nddorcom/mmx/8452.html

|

|

| Ra40では加糖米に注意 まりも 2024年6月3日(月) 22:41 |

>133MHz版には(更に)Bが付きます

おおぉそうでした。600や800などFSB 100MHz版と重なるやつに区別でBをつけたのでしたっけ。上の図のは直しておきます。800EBは6倍なのでBSEL pinを誤魔化しても黄色Cache errorになりそうですね。

ところで今さら気がつきましたが(たぶん昔にも気がついていたはずですが完全に忘却)、Ra40ではRa300/333と違って、Katmaiのうち CPUID 670と671を問答無用で排除しています。672以上しか受け付けません。理由はわかりませんが厳しめになっています。実際には搭載されたMater-Rの機種など無いにもかかわらずです。初期のKatmaiコアになにか問題ありましたっけ?

|

| L2が無くてもCACHE ERRORが出る下駄って… KAZZEZ 2024年6月9日(日) 15:22 |

> Ra40では(略)CPUID 670と671を問答無用で排除

試しにCyrixIIIのCPUID変更機能で670/671をRa40で試してみましたが…結論から言うと意味無かったです。CyrixIIIはL2キャッシュを持たないCovington相当(のフラグ持ち)CPUなので、(GenuineIntelチェックさえすり抜ければ)どんなファミリ・モデル・ステッピングIDであっても通ってしまうようでした。CPUIDを大きく変えてもCPU UPDATE DATA ERRORが出るか出ないかの違いしか確認できませんでした。L2を持つようになったC3でもL2なしフラグはそのままですので同じ挙動と思われます。

解せないのは、L2が無い(L2チェックがスルーされる)にもかかわらず、例の下駄では必ずCACHE ERRORが出る点です。このエラーの出る詳しい仕組みは存じませんが、わざわざL2チェックが終わってからL1チェックをしてエラーを起こしているんでしょうかね?

|

| CバスSCSIボードにおけるROMの信号接続 まりも 2024年6月22日(土) 20:55 |

watchスレッドで出ていた、「CバスのSCSIボードのROMをSRAMに変更して流用は可能か?」というお題での予備調査です。

ROM/RAMの切り替えパターンが残っているようなボード、TEXA HA-55BSWでは、ROM領域のリード中もライト中も、ROMのCSピンが同様に制御されていました。このことからすると、ROMの27番ピンA14を切り離してCバスのMEMW0に繋いでからSRAMに載せ替えると、書き込みができる可能性があります。FIFO転送用のSRAM 6264-7の 2個がHA-55BSWにはうまい具合に載っているので、骨までしゃぶりつくしてリサイクルできます。ただしピンの300mil幅を600に変更する必要はあります。

なおSCSI統合チップから、ROMエリアへの書き込み時にSRAMのWEに使えそうな信号は出ていないようでした。シルク印刷にはRAMと書いてありチップに繋がっているのですが、何も信号が出ていません。何かしらのソフト的制御をして書き込み可能にすれば出てくるのかもしれませんが。

いっぽう古めのDMA転送のみのボードでは、CSピンはGNDに接続されたままのものが多いようです。常に活きている訳なので、同様にSRAMのWEをCバスのMEMW0に繋げば、そのタイミングで書き込みできるように思います。

あとは実験してみるのみです。なお新しい目のボードは潰すのがもったいないので検討していません。

|

|

|